## Semi-Conductor Laboratory

# SCL CAPABILITIES AT A GLANCE

### **VISION**

- Create a strong research and development (R&D) base in the country in the field of microelectronics.

- Design & Development of devices in cutting-edge technology.

- Manufacture VLSI / MEMS-based systems & subsystems.

- Transform SCL as a Centre of Excellence in Microelectronics in the country.

### **PREAMBLE**

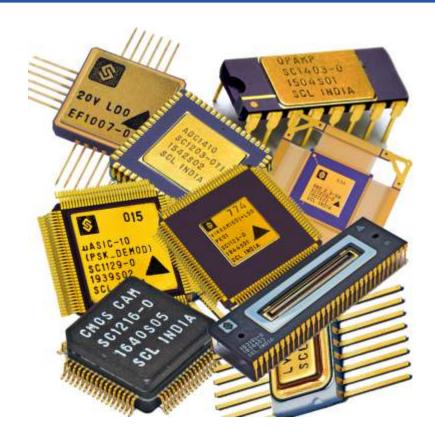

Semiconductor Laboratory (SCL), an autonomous body under the Ministry of Electronics and Information Technology (MeitY), Government of India, is the only Integrated Device Manufacturing Facility in the country providing end-to-end solutions for Development of Application Specific Integrated Circuits (ASICs), Opto-electronics devices, and Micro Electro Mechanical System (MEMS) Devices encompassing Design, Fabrication, Assembly, Packaging, Testing, and Reliability Assurance.

Formerly known as Semiconductor Complex Limited, a Government of India enterprise, it was converted into Semi-Conductor Laboratory under the Department of Space, Government of India, w.e.f. September 1, 2006. Administrative control of SCL, Society was transferred from the Department of Space (DoS) to the Ministry of Electronics and Information Technology (MeitY). SCL has an 8" wafer fab line qualified to the JEDEC-JP001A standard with a 180 nm CMOS technology node. SCL also has a 6" fab line for MEMS development and is expanding it to include a compound semiconductor fabrication facility. The VLSI design domain in SCL spreads over analog, digital, mixed-signal, memory, RF-CMOS, and optoelectronic in the form of silicon-proven and space-qualified ASICS, ASSPs, SoCs, SCL excels in developing ceramic packages and meets the demanding test requirements at the wafer & package level and reliability assurance adhere to global performance specifications such as MIL-PRF-38535 and MIL-STD-883. SCL possesses capabilities of the quality parameters of Ultra Pure Water (UPW) and bulk gases produced at SCL are at par with international standards. SCL brings decades of experience to provide customers with unparalleled microelectronics solutions in India. SCL is also engaged in the fabrication of Hi-Rel boards, Radio systems, and the indigenization of electronic subsystems.

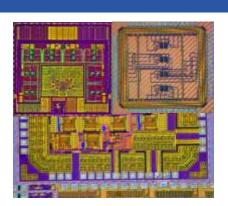

### **VLSI DESIGN**

VLSI Design activity in SCL is spread over the domains of Analog, Mixed Signal, Digital, Power, Memory, RFCMOS, and Opto-Electronic. Various designs in the form of ASICs / ASSPs / SoCs/ Test Chips have been fabricated, tested, qualified, and delivered to end users. Besides, in-house design activities are pursued for the development and enhancement of products for potential future applications. Designs have been silicon-proven and qualified to space-grade or high reliability levels for induction in space and other strategic programs, as catalogued in the products section.

### **Key Design Domains**

- Power Management

- Data Communication

- Data Converters

- Sensor Signal Conditioning

- Logic Design

- Memory

- RFCMOS

- Opto-Electronics ROIC

- RadHard By Design

- SoC

### **Design Implementation Activities**

- Feasibility Analysis

- Architecture Defining

- HDL Coding / Schematic Entry / Netlist Entry

- Electrical (Verification / Simulation)

- Synthesis

- DFT & ATPG

- Floorplan / Placement / CTS / Routing

- Full Custom Layout

- Physical Verification (DRC & LVS)

- Physical Parasitic Extraction (PEX)

- Physical STA / Post Layout Simulation

- Electro migration & IR drop analysis

- Chip Finishing & GDSII Release

- Design Automation

### **Memory Cuts & Cell Libraries**

| Туре                  | Description                                                                                                            |

|-----------------------|------------------------------------------------------------------------------------------------------------------------|

| Standard Cells        | 1.8V- Standard Cell Library (540 cells; 10 Tracks)                                                                     |

| Standard Cells (RHBD) | 1.8V- Standard Cell Library (56 cells; 30 Tracks)                                                                      |

| Memory Cuts           | SP-SRAM : 4 metal 17 cuts, 6 metal 20 cuts ; DP-<br>SRAM : 4 metal 20 cuts, 6 metal 20 cuts                            |

| I/O Cells             | 1.8V Core / 1.8V I/O ; 3.3V Core / 3.3V I/O ; 5.0V<br>Core / 5.0V I/O ; 1.8V Core / 3.3V I/O ; 1.8V Core /<br>5.0V I/O |

### **CMOS Process**

SCL has standard 180nm CMOS

baseline process technology. It enables the development of single-voltage or dual-voltage circuits requiring 1.8V, 1.8/3.3V, or 1.8V/5V power- supplies using its dual-gate oxide process, which features 4-6 Almetal layers with thick-last metal. The process has add-on modules, namely 1.8V-HVt-transistors for low leakage, high-density precision MIM capacitors (1 or 1.7 or 2.8fF/um²), high-

resistance poly (1 and 2 Kohms/sq.), Deep N-well for noise isolation, and more.

Baseline Process Technology Features

- 1.8V Core CMOS.

- 1.8V or 3.3V I/O.

- Single poly &upto 6 Metal Layers with USG-BEOL.

- 23-34 Mask layers (depending on Metal Layers and Analog modules).

Analog Process Modules

- High-Vt (Low leakage current ~one order less).

- Metal Insulator Metal capacitor: Single MIM (1 & 2fF/μm²) & stacked MIMs (2x).

- Deep N-Well (Isolated p-wells for substrate noise isolation).

- High resistance poly silicon resistor: HIPO ( $1k\Omega/sq$ ;  $2k\Omega/sq$ ).

- Thick Last metal (2μm).

- 5V-MOSFETs (Gox: 110A).

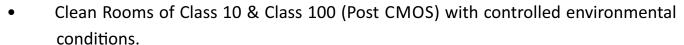

### **MEMS Fabrication Facility**

SCL has state-of-the-art 6" fab line for MEMS based devices and detector development and is expanding it to include a compound semiconductor fabrication facility for the production of optoelectronic and high-power devices.

- 6" Process Equipment Line, Inline Inspection & Metrology

- Tools and Support Utilities as per international standards.

- Dedicated bays for Wafer Fabrication Processes viz. Diffusion (High temperature furnaces), Lithography (5X stepper, 1X aligner, coater developer track), Etching (Dry & Wet), Implantation (High and medium current implanters), Thin Films (PVD & CVD furnaces for dielectrics and metals) working seamlessly from Wafer-in to Wafer-out.

- MEMS Specific fabrication capabilities like wafer bonding, electroplating, glass wafer processing, Vapor HF, CPD etc.

- Characterization facility including Laser Doppler Vibrometer, Nanoindentor, AFM,

XRD, 4 Point Probe resistance measurement.

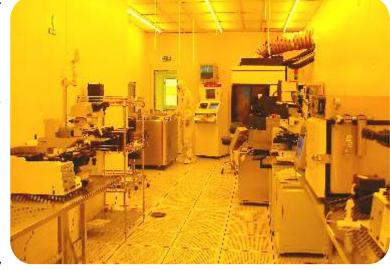

### **VLSI ASSEMBLY & PACKAGING**

VLSI and MEMS Packaging facility operating in Class 100 and Class 10000 Clean Rooms includes Die Bonders, Ball and Wedge Wire Bonders, Multi-Zone Furnaces for Hermetic Sealing, Multi Function Bond Pull Testers, Laser Welder, Dicing Saw, Tape Mounter etc.

### **Key capabilities**

- Package design lab catering the bonding and device drawing generations for all devices for post Fab activities.

- Design and analysis of Single die and multi-die substrates (SiP) to optimise the Signal and Power Integrity performances for CMOS, Imager & RF devices.

- Design, analysis and development for MEMS packaging

- Thermo mechanical design, analysis & characterisation for devices

- Layout of IC package and generation of fabrication inputs for developing custom package.

- Standard IC packages and Custom Substrate development end to end solutions.

- Fine Pitch Bonding capability (using 0.8,1 &1.25mil wire) for pad size of 57μmx57μm and 65μm pitch

- Low Temperature Process for packaging large dies of Imager devices

- Multi-Chip Packaging Process for ASICs and sensor devices

### **VLSI TEST FACILITY**

VLSI and MEMS Test Facilities meet the demanding test requirements of complex, high-speed, and high-pin count Integrated Circuits in the digital, mixed-signal, and Analog domains. The Facility also caters to the testing of a variety of MEMS and RF devices, such as Pressure, Temperature & Humidity Sensors, Accelerometers, RF switches, and Band-Pass Filters.

Test plans and engineering activities implemented at various stages of product development include:

- Prototype Testing/Debug at wafer and device level

- Post Silicon Validation and characterization

- Production testing on Automatic Test Equipment

### **Key capabilities**

- Class 10000 clean room with 8" and 6" Automatic Wafer Prober, VLSI Testers, Temperature characterization setup, MEMS device test setups including Shaker, Laser Doppler Vibrometer (LDV), Thermal Chamber, Pressure calibrator etc.

- Capability to build semi-automatic test setups for electrical design validation and characterisation of CMOS and MEMS devices. Various such test setups for CMOS ASICS, CCD detectors and Low Drop Out Regulators, Process Evaluation

- Vehicles like Ring Oscillators and Band Gap Reference Circuits have been developed in-house.

- In-house development capability to develop blade-type probe cards up to 120-pin up to 90μm pad pitch. We have design capability of developing high-pin count epoxy probecards with pitch upto 65μm exceeding 400 pads.

- Characterization of Digital, Mixed Signal and Analog devices from -55°C to 125°C up to 512 I/O's (800 MHz clock rate)Expertise to develop Test Programs for variety of devices such as amp etc.

- Design capability for multilayer & high speed Device Interface Boards and Prober Interface Boards

- Characterization of Pressure Sensors (up to 600 bar), Temperature Sensors (-90°C to 180°C), Humidity Sensors (10% RH to 95% RH) & Accelerometers (up to 20g)

- Programming languages like C, C#, Visual Basic, MATLAB, LabView etc. have been used to develop test programs on various testers to test digital, analog and mixed-signal CMOS devices.

### **RF TEST FACILITIES**

SCL has in-house testing capability for RF circuits for both wafer level and package level up to 40 GHz. Full RF and DC characterizations can be carried out inhouse. The capabilities of major equipment are mentioned below:

- Vector Network Analyzer VNA):

- Spectrum Analyzer: Up to 26.5GHz with Noise Figure measurement

- Signal Generator: 250 KHz to 40GHz , +4dBm to -130dBm, Modulation-Amplitude Frequency & Phase

- Impedance Analyzer: 1 MHz to 3 GHz, Measurements |Z|,|Y|, Ls,Lp,Cs,Cp,Rs, Rp,X,G,B,D,Q,<sup>γ</sup>l z, Er, μr, tan?

- Power Meter: DC-40 GHz, -30 dBm to + 20 dBm

- RF Prober: Manual (Summit 11K) and Semi-Automatic (Summit12K) RF Prober with thermal control chuck

### **MEMS TEST FACILITIES**

SCL has in-house testing capability for MEMS circuits. The capabilities of major equipment are mentioned below:

Temperature Calibrator:-

### **Temperature Range:-**

-35ºC to 100ºC (Ethanol)

35°C to 280°C (Silicon Oil)

**Reference High Precision PRT**

Temperature Range: -200 ºC to 661 ºC

Basic Accuracy: ± 0.006 at 0°C

- VibShaker:-Max. Acceleration: 110g; Frequency range: 7KHz

- Laser Doppler Vibrometer

- Wafer Prober

- Pressure Controller / Calibrator:-

Upto 200 Bar (Automatic Calibrators):

1.6 Bar

1.6 bar, 20 Bar

50 Bar

70 mBar, 200 Bar upto 600 Bar (Manual, Dead Weight Calibrator)

- Vacuum Pumps

- Temperature Chambers

- Temperature Range: -70°C to 180°C; Accuracy: ±0.5°C

### **RELIABILITY & QUALITY ASSURANCE**

The Reliability & Quality Assurance of the devices / boards / sub-systems / systems manufactured at SCL is maintained throughout design, chip fabrication, assembly / packaging and testing phases. Regular inline QA inspection / audits are carried out to ensure defect

free manufacturing. Screening and qualification of products for required applications is an integral part of the process. The reliability and quality assurance requirements are guided by global performance specifications as per MIL-PRF-38534, MIL-PRF-38535, JEDEC, MIL-883 and other relevant standards. Continuous improvements in processes are implemented through feedbacks at appropriate stages and performing failure analysis.

### Facility for Environmental Test

- Process Reliability Test System.

- Thermal Shock Chamber (Air to Air).

- Thermal Shock Chamber (Liquid-to-Liquid).

- Vibration Test System.

- High Temperature, High Humidity Chamber.

- Fine & Gross Leak Test Systems for Hermeticity Check.

- Life Operating Test Systems (Burn-In Chambers).

- Constant Acceleration Test System.

- Mechanical Shock Tester.

- Particle Impact Noise Detection (PIND) Tester.

- Electro Static Discharge (ESD) Simulator based on Human Body Model (HBM).

### **Facility for Environmental Test**

- Scanning Electron Microscope (SEM).

- Focused Ion Beam System (FIB).

- Energy Dispersive X-Ray Spectrometer (EDX).

- Micro Cleaver.

- Polisher Grinder.

- Optical Microscopes.

### **Key Capabilities**

- Screening & Qualification of VLSI devices / ASICs / MEMS devices / boards / subsystems / systems.

- Process Qualification.

- Device Failure Analysis.

- Process Audits.

- Quality System & Documentation Control.

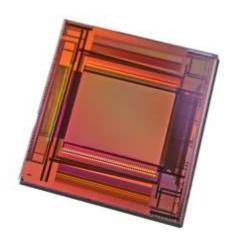

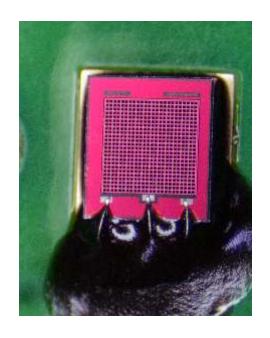

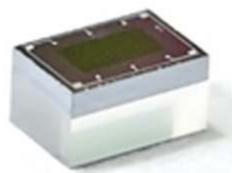

### **ELECTRO-OPTICS/DETECTOR TECHNOLOGY**

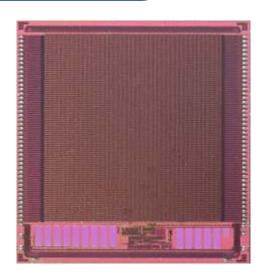

SCL has a long established fabrication process for Silicon Charge Coupled Device (CCD) based image sensors in the visible range (400nm to 1000nm) for remote sensing for cartography and resource mapping applications.

These detectors are also to be used for satellite attitude and orbital control in the form of star sensors.

Facility is in place for bare detectors, assembly, testing and flight qualification of Detectors.

### **Key Detectors developed include**

- Photodiode detector based CCD linear imager with 4K elements for Indian Mini Satellite (IMS-1).

- Further 1K x 1K Frame Transfer CCD image sensor for star sensor applications and is flight qualified for space use.

- Hyperspectral image sensor fabricated in SCL with a 1000 (spatial) x 66 (spectral) for HySIS satellite.

- 4000 element x 48 stage Frame Transfer CCD sensors in Thirteen different bands for the Ocean Colour Monitor (OCM-3) payload of Oceansat-3 is under qualification.

- SCL has also worked in collaboration with other strategic organizations to develop Silicon Photomultiplier (SiPM) and large area diode sensors for various scientific and other applications.

- Current efforts to further enhance the existing technology by introducing anti-blooming capabilities, enhancing short wavelength response and increasing radiation hardness which will allow the use of detectors developed in SCL, in more demanding applications.

# SCL PRODUCTS

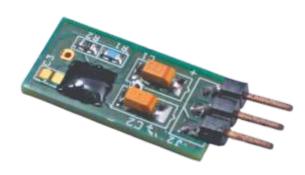

### LOW DROP-OUT LINEAR VOLTAGE REGULATOR 1.2V, 1.6A

### **PRODUCT DESCRIPTION:**

This LVR supplies a nominal voltage of 1.2V to a circuit or load. The output voltage of the voltage regulator is regulated by the internal circuitry of the regulator to be relatively independent of the current drawn by the load, the supply or line voltage, and the ambient temperature. It is stable with an external capacitor not lower than 10uF of ESR 10hm to 10ohm. In order to protect voltage regulator from excessive temperatures or accidental short circuit, Over-temperature shutdown and programmable Over-current shutdown circuit are included in this chip.

- Nominal V<sub>OUT</sub>: 1.2V

- Maximum output current: 1.6A

- Dropout Voltage at full load < 400mV</li>

- Line regulation: < 2%/V; Load regulation: < 1%</li>

- Quiescent current (I<sub>GND</sub>): 14mA

- Max Supply V<sub>IN</sub>: 3.6V

- Power Good Flag: -5% of V<sub>NOM</sub>

- Over temperature shutdown with Disable Feature

- Programmable Short Circuit Current Shutdown after 1 sec delay

- Operating Temperature (T<sub>△</sub>): -55°C to +125°C

- SCL's 180nm CMOS Technology

- Dies/Customized Package Options

### LOW DROP-OUT LINEAR VOLTAGE REGULATOR 1.8V, 150mA

### **PRODUCT DESCRIPTION:**

This LVR provides a fixed output voltage of 1.8V, 150mA full load current. It is stable with an external capacitor not lower than 4.7uF of ESR 1 ohm to 10 ohm. It supplies a nominal voltage of 1.8V to a circuit or load. The output voltage of the voltage regulator is regulated by the internal circuitry of the regulator to be relatively independent of the current drawn by the load, the supply or line voltage, and the ambient temperature. In order to protect voltage regulator from excessive temperatures or accidental short circuit, Overtemperature and Over-current protection circuit are included in this chip. Power good pin indicates whether output is within range of ±10% of nominal output.

- Nominal V<sub>out</sub>: 1.8V

- Maximum output current: 150mA

- Dropout Voltage at full load: < 400mV</li>

- Quiescent current (IGND): 9mA

- Voltage accuracy line and load: <0.5%</li>

- Power Good feature: ± 10% of V<sub>NOM</sub>

- Max Supply VIN: 3.6V

- Over temperature shutdown with Disable Feature

- Short circuit current limiting feature: 350mA

- Operating Temperature (TA): -55°C to +125°C

- SCL's 180nm CMOS Technology

- Dies/Customized Package Options

### LOW DROP-OUT LINEAR VOLTAGE REGULATOR 1.8V, 800mA

### **PRODUCT DESCRIPTION:**

This LVR provides a fixed output voltage of 1.8V, 800mA full load current. It is stable with an external capacitor not lower than 10uF of ESR 1 ohm to 10 ohm. It supplies a nominal voltage of 1.8V to a circuit or load. The output voltage of the voltage regulator is regulated by the internal circuitry of the regulator to be relatively independent of the current drawn by the load, the supply or line voltage, and the ambient temperature. In order to protect voltage regulator from excessive temperatures or accidental short circuit, Overtemperature and Over-current protection circuit are included in this chip. Power good pin indicates whether output is within range of -5% and +10% of nominal output.

- Nominal V<sub>OUT</sub>: 1.8V

- Maximum output current: 800mA

- Dropout Voltage at full load: < 200mV</li>

- Quiescent current (I<sub>GND</sub>): 10mA

- Voltage accuracy line and load: <1%</li>

- Power Good feature: -5% and+10% of V<sub>NOM</sub>

- Max Supply V<sub>IN</sub>: 3.6V

- Over temperature shut down with Disable Feature

- Programmable Short circuit current limiting feature

- Operating Temperature (T<sub>△</sub>): -55°C to +125°C

- SCL's 180nm CMOS Technology

- Dies/Customized Package Options

### LOW DROP-OUT LINEAR VOLTAGE REGULATOR 1.8V, 1.6A

### **PRODUCT DESCRIPTION:**

This LVR supplies a nominal voltage of 1.8V to a circuit or load. The output voltage of the voltage regulator is regulated by the internal circuitry of the regulator to be relatively independent of the current drawn by the load, the supply or line voltage, and the ambient temperature. In order to protect voltage regulator from excessive temperatures or accidental short circuit, Overtemperature shutdown and programmable Overcurrent shutdown circuit are included in this chip. It is stable with an external capacitor not lower than 10uF of ESR 10hm to 10ohm.

- Nominal V<sub>out</sub>: 1.8V

- Maximum output current: 1.6A

- Dropout Voltage at full load < 300mV</li>

- Line regulation: < 2%</li>

- Load regulation: <1%</li>

- Quiescent current (I<sub>GND</sub>): 14mA

- Max Supply V<sub>IN</sub>: 3.6V

- Power Good: -5% of V<sub>NOM</sub>

- Over temperature shutdown with Disable Feature

- Programmable Short Circuit Current Shutdown after 1sec delay

- Operating Temperature (T₄): -55°C to +125°C

- SCL's 180nm CMOS Technology

- Dies/Customized Package Options

### LOW DROP-OUT LINEAR VOLTAGE REGULATOR 3.3V, 200mA

### **PRODUCT DESCRIPTION:**

The 3.3 V output, 200mA full load current LVR provides a fixed output voltage of 3.3 V for a wide range of input operating voltage from 3.7 V to 6 V. The LVR is stable with an external capacitor not lower than 4.7uF of ESR 0.1 ohm to 10 ohm. SC1019-0 is mainly intended for integration with digital, analog and RF chips.

In order to protect voltage regulator from excessive temperatures or accidental short circuit, Overtemperature protection circuit and short circuit foldback current limiting feature are included in this chip. Device will go in to Short circuit fold-back at twice of FL, i.e., 0.4A.

- Nominal V<sub>OUT</sub> = 3.3V

- Full load current = 200mA

- Low guiescent current of <1 mA</li>

- Dropout Voltage at full load < 150mV</li>

- Max Supply V<sub>IN</sub>: 6V

- Over temperature shut down mechanism

- Short circuit fold-back current limiting feature: 400mA

- Operating Temperature (T<sub>△</sub>): -55°C to +125°C

- SCL's 180nm CMOS Technology

- Packaged in COB package

- Dies/Customized Package Options

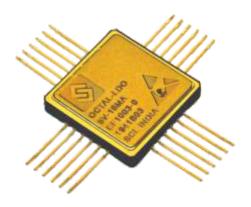

### OCTAL-CORE LOW DROP-OUT LINEAR VOLTAGE REGULATOR 5V, 16mA

### **PRODUCT DESCRIPTION:**

The LVR has independent supplies a nominal voltage of 5V to a circuit or load, and it can deliver up to 16 mA per channel of output current. Internally, this linear regulator consists of a reference, an error amplifier, and a P-channel MOSFET pass transistor. It has 8 independent cores.

- Nominal output voltage: 5V

- Eight Independent Cores

- Maximum output current per core: 16mA

- Dropout voltage: 500mV

- Voltage accuracy over line & load: 1%

- Fold back current at 19mA

- Fold back recovery at 5mA

- Max Supply V<sub>IN</sub>: 7.5V

- Operating Temperature (T₄): -55°C to +125°C

- 24 Pin CFP/ Customized Package Options / Die

### PROGRAMMABLE BIAS GENERATOR, 0.5V-2.1V, 8-Bits, 5mA

### **PRODUCT DESCRIPTION:**

It is 8-bit programmable dual channel output bias voltage generator with dynamic range of 1.6V (0.5V to 2.1V). It has band-gap reference block, voltage reference block, two R-2R DACs; two band limited operational amplifier. It has a four wire serial interface. The digital input byte is converted to corresponding analog output with help of DAC (Digital to Analog Converter).

### **FEATURES:**

Line voltage: 3.0V-3.6V

Dynamic range: 1.6V (0.5V to 2.1V)

Resolution: 8bits

Output drive current per channel: 5mA

Two Programmable outputs

Output enable/disable feature

Programming Interface: 4wire serial

• Clock input: LVCMOS compatible

Low Power Dissipation

Operating Temperature (T₁): -55°C to +125°C

SCL's 180nm CMOS Technology

Packaged in 20 Lead Side Brazed package

FM Qualified as per MIL STD 883

### HIGH VOLTAGE, QUAD SOLID STATE SWITCH 27V-42V, 1.0A

### **PRODUCT DESCRIPTION:**

It has four independent switches in a single die. It can switch 1A load at 42V. This switch transistor is controlled through a control circuit. The control circuit operates from input voltage. When the control input is high (5V), the switch conducts and provides the load current (1A). Otherwise this switch remains off. The input voltage may be as low as 3.5V to be considered as High (>3.5V) which can turn on transistor.

- Raw bus voltage: 27V-42V

- Full load current: 1A

- Control voltage: 3.5V to 5.5V

- Output drop (VSD): < 650mV at 1A</li>

- Input (leakage) current: 0.19mA

- Quiescent current (IGND): 40nA

- Operating Temperature (T₁): -55°C to +125°C

- Packaged in 48 Pin CFP

# DATA CONVERTERS (ADC & DAC)

### 16-BIT, 5 MSPS, PIPELINE ANALOG TO DIGITAL CONVERTER WITH ON CHIP VOLTAGE REFERENCE

### **PRODUCT DESCRIPTION:**

The 16-bit, 5-MSPS is a monolithic CMOS analog-to-digital converter capable of converting analog input signals into 16-bit digital word at 5 Mega samples per second (MSPS) and designed for imaging applications. This converter uses a differential, pipeline architecture with digital error correction. Operating on a single 3.3V power supply, device achieves ≥ 13-bits effective resolution at Nyquist rate and consumes <130mW. The Power Down feature reduces power consumption to <15mW. The differential inputs provide a full scale differential input swing equal to 4 times of VREF (4\*(CAPTE-CAPBE)). Full scale input range is recommended for optimum performance.

- OperatingVoltage:3.3V±0.3V

- Resolution: 16-Bit

- Data Rate: 5MSPS

- Input Range : 2Vp-p Diff. /Single Ended

- On-Chip Voltage References

- No missing code Guaranteed

- Output Data Format: Straight Binary

- Data Latency: 7 Clock Cycles

- Power Consumption < 130mW

- Power Down Mode

- Operating Temperature (T₄): -55°C to +125°C

- SCL's 180nm CMOS Technology

- Package: 68 PIN CQFP-J

- θic: 4.81° C/W

### 14-BIT, 10MSPS, PIPELINE ANALOG TO DIGITAL CONVERTER WITH ON CHIP VOLTAGE REFERENCE

### **PRODUCT DESCRIPTION:**

The 14-bit 10-MSPS is a monolithic CMOS analog-to-digital converter capable of converting analog input signals into 14-bit digital word at 10 Mega samples per second (MSPS) and designed for imaging applications. This converter uses a differential, pipeline architecture with digital error correction. Operating on a single 3.3V power supply, device achieves > 12-bits effective resolution at nyquist rate and consumes <250mW power. The Power Down feature reduces power consumption to <50mW. The differential inputs provide a full scale differential input swing equal to 4 times of VREF (4\*(CAPTE-CAPBE)). Full scale input range is recommended for optimum performance. The ASIC is fabricated in 0.18μm SCL CMOS Standard Logic Process.

- OperatingVoltage:3.3V

- Resolution: 14-Bit

- Data Rate: 10MSPS

- Input Range :2Vp-p Differential /Single Ended

- On Chip Voltage References

- No missing code Guaranteed

- Output Data Format: Straight Binary

- Data Latency: 8 Clock Cycles

- Power Consumption < 250mW</li>

- Power Down Mode

- SCL's 180nm CMOS Technology

- Operating Temperature (T<sub>A</sub>): -55°C to +125°C

- Package:68 PIN CQFP-J

- θjc: 4.81° C/W

### 14-BIT, 5MSPS, LOW POWER PIPELINE ANALOG TO DIGITAL CONVERTER

### **PRODUCT DESCRIPTION:**

The 14-bit 5 MSPS is a monolithic CMOS analog-todigital converter capable of converting analog input signals into 14-bit digital word at 5 Mega samples per second (MSPS) and designed for imaging applications. This converter uses a differential, pipeline architecture with digital error correction. Operating on a single +3.3V power supply, device achieves >12.0 bits effective resolution at nyquist rate and consumes <100mW. The Power Down feature reduces power consumption to 50mW. The differential inputs provide a full scale differential input swing equal to 4 times of VREF (=CAPTE-CAPBE). Full scale input range is recommended for optimum performance. The chip requires three external references as 1.9V, 1.65V and 1.4V. The device has on chip voltage reference. To use internal reference, external buffer must be provided between internal and external references.

- OperatingVoltage:3.3V

- Resolution:14-Bit

- DataRate:5MSPS

- 2Vp-p Differential/Single Ended Input

- No Missing Code guaranteed

- Data Latency 8 Clock Cycles

- Output straight Binary Format

- Power Consumption < 100 mW

- Power Down Mod

- SCL's 180nm CMOS Technology

- Operating Temperature (T<sub>Δ</sub>): -55°C to +125°C

- 68 PIN CQFP-J Package

- θjc: 4.81° C/W

### 12-BIT, 8MSPS LOW POWER PIPELINE ANALOG TO DIGITAL CONVERTER

### **PRODUCT DESCRIPTION:**

The 12-bit 8 MSPS is a monolithic CMOS analog-todigital converter capable of converting analog input signals into 12-bit digital word at 8 Mega samples per second (MSPS) and designed for imaging applications. This converter uses a differential, pipeline architecture with digital error correction. The Power Down feature reduces power consumption to 50 mW. The differential inputs provide a full scale differential input swing equal to 4 times of VREF(= CAPTE - CAPBE). Full scale input range is recommended for optimum performance. The chip requires three external references as 1.9V, 1.65V and 1.4V. The device has on chip voltage reference. To use internal reference, external buffer must be provided between internal and external references. The chip requires three external references as 1.9V, 1.65V and 1.4V. The device has on chip voltage reference. To use internal reference, external buffer must be provided between internal and external references

- OperatingVoltage:3.3V

- Resolution:12-Bit

- Data Rate: 8MSPS

- 2Vp-p Differential/Single Ended Input

- No Missing Code guaranteed

- Output straight Binary Format

- Data Latency 8 Clock Cycles

- Power Consumption <110mW

- Power down Mode

- SCL's 180nm CMOS Technology

- Operating Temperature (T<sup>A</sup>): -55ºC to +125ºC

- 68 PIN CQFP-J Package

- θic: 4.81° C/W

### 8-BIT, 50MSPS, LOW POWER, PIPELINE ANALOG TO DIGITAL CONVERTER

### **PRODUCT DESCRIPTION:**

The 8-bit 50MSPS is a monolithic CMOS analog-todigital converter capable of converting analog input signals into 8-bit digital word at 50 Mega samples per second (MSPS) and designed for imaging and communication applications. The converter uses a differential, pipeline architecture with digital error correction. Operating on a single 3.3V power supply, device achieves 8-bits effective resolution at nyquist rate and consumes <420mW power. The Power Down feature reduces power consumption to <15mW. The differential inputs provide a full scale differential input swing equal to 4 times of VREF (4\*(CAPTE-CAPBE)). Full scale input range is recommended for optimum performance. The chip requires three external references as 1.9V, 1.65V and 1.4V. The device has on chip voltage reference. To use internal reference, external buffer must be provided between internal and external references

- Operating Voltage:3.3V

- Resolution: 8-Bit

- Data Rate: 50MSPS

- 2Vp-p Differential/Single Ended Input

- On Chip Voltage References

- No Missing Code guaranteed

- Output straight Binary Format

- Data Latency 4 Clock Cycles

- Power Consumption < 420mW</li>

- Power Down Mode

- SCL's 180nm CMOS Technology

- Operating Temperature (T₄): -55°C to +125°C

- 64 PIN CQFP Package

- θjc: 4.03° C/W

### 8-BIT, 1MSPS SUCCESSIVE APPROXIMATION ANALOG TO DIGITAL CONVERTER

### **PRODUCT DESCRIPTION:**

The 8-bit SAR is a monolithic CMOS analog-to-digital converter capable of converting analog input signals into 8-bit digital word at 1 Mega samples per second (MSPS) and designed for imaging applications. This converter uses a SAR architecture, operating on a single 3.3V power supply, device achieves 8-bits effective resolution at nyquist rate and consumes <10mW power. The inputs provide a full scale input swing equal to 3.3V. Full scale input range is recommended for optimum performance. The ASIC is fabricated in 0.18µm SCL CMOS Standard Logic Process.

### **FEATURES:**

Operating Voltage: 3.3V

Resolution: 8-BitData Rate: 1MSPS

Input Range: 3.3Vp-p Single Ended

No missing code Guaranteed

Output Data Format: Straight Binary

Power Consumption < 10mW</li>

SCL's 180nm CMOS Technology

Operating Temperature (T<sup>A</sup>): -55°C to +125°C

Packaged in 64 Pins, CQFP

• θjc: 4.03° C/W

### 12-BIT,1MSPS, 4-CORE SUCCESSIVE-APPROXIMATION -REGSITER(SAR) ANALOG TO DIGITAL CONVERTER

### **PRODUCT DESCRIPTION:**

The 8-bit SAR is a monolithic CMOS analog-to-digital converter capable of converting analog input signals into 8-bit digital word at 1 Mega samples per second (MSPS) and designed for imaging applications. This converter uses a SAR architecture, operating on a single 3.3V power supply, device achieves 8-bits effective resolution at nyquist rate and consumes <10mW power. The inputs provide a full scale input swing equal to 3.3V. Full scale input range is recommended for optimum performance. The ASIC is fabricated in 0.18µm SCL CMOS Standard Logic Process.

### **FEATURES:**

• Operating Voltage: 3.3V

Resolution: 8-BitData Rate: 1MSPS

• Input Range: 3.3Vp-p Single Ended

• No missing code Guaranteed

Output Data Format: Straight Binary

Power Consumption < 10mW</li>

• SCL's 180nm CMOS Technology

• Operating Temperature (TA): -55°C to +125°C

• Packaged in 64 Pins, CQFP

• θjc: 4.03° C/W

### 14-BIT, 10MSPS CCD ANALOG SIGNAL PROCESSOR WITH ON CHIP VOLTAGE REFERENCE

### PRODUCT DESCRIPTION:

This is fully integrated, high performance analog signal processor for CCD applications. It features a single channel architecture designed to sample and conditions the outputs of CCD arrays. Signal paths utilize Correlated Double Sampler (CDS), 6-bit Programmable Gain Amplifiers (PGA), and 9-bit offset correction DAC for black level correction of input. The PGA and offset DAC are programmed independently allowing unique values of gain and offset for inputs. The internal registers can be programmed through a 4-wire serial digital interface. A programmable feature includes gain adjustment, black level correction, programmable delay and input bandwidth control. This converter uses a differential, pipeline architecture with digital error correction. The Power Down feature reduces power consumption to 25mW. The differential inputs provide a full scale differential input swing equal to 2 times of VREF (=CAPTE-CAPBE).

- Operating Voltage: 3.3V

- Resolution: 14Bits

- Data Rate: 10MSPS

- 1Vp-p Differential /Single Ended Input

- On Chip Voltage References

- No Missing Code Guaranteed

- Output straight Binary Format

- Data Latency 9 Clock Cycles

- Power Consumption < 250mW</li>

- Power Down Mode

- 64 PGA Gain Steps 1 to 6 PGA Gain Ranges

- 9Bit Offset Correction

- ±60mV Offset Correction

- SCL's 180nm CMOS Technology

- 100 PIN CQFP Package

- θjc: 0.99° C/W

### SINGLE CHANNEL, 12-BIT,5MSPS CCD ANALOG SIGNAL PROCESSOR

### PRODUCT DESCRIPTION:

This is fully integrated, high performance analog signal processor for CCD applications. It features a single channel architecture designed to sample and conditions the outputs of CCD arrays. Signal paths utilize Correlated Double Sampler (CDS), 6-bit Programmable Gain Amplifiers (PGA), and 9-bit offset correction DAC for black level correction of input. The PGA and offset DAC are programmed independently allowing unique values of gain and offset for inputs. The internal registers can be programmed through a 4-wire serial digital interface. A programmable feature includes gain adjustment, black level correction, programmable delay and input bandwidth control. This converter uses a differential, pipeline architecture with digital error correction. The Power Down feature reduces power consumption to 25mW. The differential inputs provide a full scale differential input swing equal to 2 times of VREF (=CAPTE-CAPBE). The chip requires three external references as 1.9V, 1.65V and 1.4V. The device has on chip voltage reference. To use internal reference, external buffer must be provided between internal and external references.

- Operating Voltage: 3.3V

- Resolution: 12Bits

- Data Rate: 5MSPS

- 1Vp-p Differential / Single Ended Input

- On Chip Voltage References

- No Missing Code Guaranteed

- Output straight Binary Format

- Data Latency 9 Clock Cycles

- Power Consumption < 170mW

- Power Down Mode

- 64 PGA Gain Steps 1 to 6 PGA Gain Ranges

- 9Bit Offset Correction DAC Resolution

- ±60mV Offset Correction DAC Range

- SCL's 180nm CMOS Technology

- 100 PIN CQFP Package

- θjc: 0.99° C/W

### 12 BIT, 20MSPS DIGITAL TO ANALOG CONVERTER

### **PRODUCT DESCRIPTION:**

The SC1605 is a two channel (complementary output) precision fully integrated 12 bit digital to analog converter with full scale current of 2mA. It has got an on chip precise low drift voltage reference of 1.2V. There is an option of disabling the on chip reference to apply external reference. Latches are provided for high speed synchronization providing better AC characteristics for DAC. Additional option is provided for disabling the latches in case latches have to be bypassed. On chip power on reset is also provided so that the chip output doesn't go to unknown state at the time of power on.

### **FEATURES:**

Operating Voltage: 3.3V

Resolution: 12 Bits

Data Rate: 20MSPS

- 2mA Full Scale Input Range

- Power Down Mode

- Monotonicity Guaranteed

- Power On Reset

- On Chip 1.2V Reference

- Power Down Feature

- SCL's 180nm CMOS Technology

- 64 Pin CERQUAD Package

- θjc: 3.77° C/W

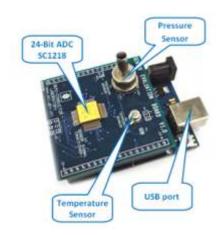

### 4 CHANNELS, 24-BIT Σ-Δ ANALOG TO DIGITAL CONVERTER (RADIATION HARDENED)

### **PRODUCT DESCRIPTION:**

The SC1218-0 is a precision, wide range, Sigma-Delta, Analog-to-Digital converter with 24-bit resolution operating from 3.0V to 3.6V. It has fully four differential multiplexed channels. The PGA (Programmable Gain Amplifier) provides selectable gains of 1 to 128 in binary steps with an effective resolution of 19 bits at PGA 1 and OSR of 2048. It uses a second order Sigma Delta Modulator that converts the analog input signal in to a digital pulse train whose average duty cycle represents the digitized signal information. The pulse train is then processed by a digital sinc3 filter to produce a digital output. The decimation ratio of the digital filter can be programmed by user either to achieve higher accuracy or higher throughput. SC1218-0 has digitally on-chip offset and gain calibration. The serial interface is SPI Compatible. It can be configured to scan all the signal input sequentially with minimum communication overhead.

- 24 BITS NO MISSING CODES1

- 0.003% INL

- 19 BITS EFFECTIVE RESOLUTION (PGA = 1, OSR=2048)

- 12 BITS (PGA = 128, OSR=2048)

- PGA FROM 1 TO 128 (BINARY STEPS)

- PROGRAMMABLE DATA OUTPUT RATES UP TO 20KSPS

- PRECISION ON-CHIP 1.22V REFERENCE ACCURACY: 1.5%

- DRIFT: ±20ppm of REFOUT

- EXTERNAL DIFFERENTIAL REFERENCE Upto 2.5V

- ON-CHIP CALIBRATION

- SPI COMPATIBLE

- 3.0V TO 3.6V

- RAD HARDENED (TID) UPTO 300KRAD

- SEL/SEU IMMUNE UPTO 50 LET MEV-cm2/mg

- 180nm SCL CMOS STANDARD LOGIC PROCESS

- ESD PROTECTION UPTO ±3KV HBM

- $\Theta_{1C} = 3.7^{\circ} \text{C/W}$

# 4 CHANNELS, 24-BIT $\Sigma$ - $\Delta$ ADC WITH INPUT OFFSET DAC (RDAS)

#### **PRODUCT DESCRIPTION:**

The RDAS is a precision, wide range, Sigma-Delta, Analog-to-Digital converter with 24-bit resolution operating from 2.97 V to 3.6V for sensor signal conditioning application. It has fully four differential multiplexed channels. The PGA (Programmable Gain Amplifier) provides selectable gains of 1 to 128 in binary steps with an effective resolution of 19 bits at PGA 1 and OSR of 2048. It uses a second order Sigma Delta Modulator that converts the analog input signal in to a digital pulse train whose average duty cycle represents the digitized signal information. The pulse train is then processed by a digital sinc3 filter to produce a digital output. The decimation ratio of the digital filter can be programmed by user either to achieve higher accuracy or higher throughput. SC1213-0 has digitally on-chip offset and gain calibration. It also contains 8 Bits Input offset DAC for adjusting the offset and two 8-bits current DAC with three different ranges. The serial interface is SPI Compatible.

- 4 Multiplexed Differential Input Channel

- 24 Bits Σ-Δ ADC

- No missing code

- PGA from 1 to 128 (Binary Steps)

- 8-Bit Input Offset DAC at each PGA

- Two 8 Bits IDAC (three different range)

- INL: 0.020%

- 19 Bits ENOB (PGA = 1, OSR=2048)

- 12 Bits ENOB (PGA = 128, OSR=2048)

- Programmable Data Rate upto 5KSPS

- Precision on-chip 1.22V Reference Accuracy: 1.0%, Drift: ±40ppm

- On-chip Calibrations

- SPI Compatible

- 2.97V TO 3.6V

- POWER CONSUMPTION < 10mW</li>

#### 16 CHANNELS SIMULTANEOUS SAMPLING 24 BIT Σ-Δ ADC (MULTI-CORE RDAS1.1)

#### **PRODUCT DESCRIPTION:**

Multi-Core Reconfigurable Data Acquisition System (Multi-Core RDAS) is a fully integrated data acquisition system. It incorporates 16 high resolution Sigma Delta ( $\Sigma\Delta$ ) ADCs, 32 Eight Bits IDACs along with the calibration and over-range detection unit for each  $\Sigma\Delta$  ADC. User can communicate with any of the ADC through SPI interface using four bits channel address. There are two modes of operation: Program mode and Flight mode. User can select any of the modes through a primary input pin. During Program Mode, user can program all the ADC cores and IDACs and during flight mode user can read the data continuously.

Each  $\Sigma\Delta$  ADC uses a second order modulator with a Programmable Gain Amplifier (PGA) and on-chip offset and gain calibration.  $\Sigma\Delta$  Modulator converts the analog input signal into a single bit stream of 1s and 0s where the density of 1s and 0s represents the digitized information. The single bit data from modulator is then processed by a digital Sinc3 filter to produce a 24 bits digital output. The output data rate of  $\Sigma\Delta$  ADC is programmable. Each 8-bits current DAC is available with three different ranges: 0.5mA, 1mA and 2mA.

- Sixteen ΣΔ ADCs

- 24 Bits resolution

- No missing code1

- PGA from 1 to 128 (Binary Steps)

- Programmable Output Data Rate

- INL:0.005%

- 19 Bits ENOB (PGA = 1, OSR=2047)

- On-chip Offset and Gain Calibrations

- Data Format Selection

- Thirty Two IDACs

- 8 Bits resolution

- Programmable Full Scale Ranges of 0.5 mA, 1mA and 2mA.

- Precision on-chip 1.22V Reference

- Accuracy: 1.7%, Drift: ±80ppm

- On Chip 1.8V Voltage Regulator

- Program and Flight Mode Operation

- SPI Compatible

- Supply Voltage 3.0V TO 3.6V

- 180nm SCL CMOS standard logic process

- θJC =0.88°C/W

# Octal-Core High Frequency Reconfigurable Data Acquisition System (OC HFRDAS)

#### **DESCRIPTION:**

Octal-Core High frequency Reconfigurable Data Acquisition System (OC HF RDAS) is a fully integrated data acquisition system. It incorporates 8 high resolution Sigma Delta ( $\Sigma\Delta$ ) ADCs along with the calibration and over-range detection unit for each  $\Sigma\Delta$  ADC. User can communicate with any of the ADC through SPI interface using three bits channel address. There are two modes of operation: Program mode and Flight mode. User can select any of the modes through a primary input pin. Each ΣΔ ADC uses a second order modulator with a Programmable Gain Amplifier (PGA). The  $\Sigma\Delta$  modulator converts the analog input signal into a digital pulse train whose average duty cycle represents the digitized signal information. The pulse train is then processed by a digital sin 5 filter to produce a digital output. The output data rate of  $\Sigma\Delta$  ADC is programmable.

- Eight ΣΔ ADCs

- 24 Bits resolution

- PGA from 1 to 128 (Binary Steps)

- Programmable Data Rate

- INL:0.01%

- 19 Bits Effective Resolution (PGA = 1, OSR=2047)

- On-chip Offset and Gain Calibrations

- Over Range Detection

- Data Format Selection

- Precision on-chip 1.22V Reference

- Accuracy: ±2.5%, Drift: 50ppm/°C

- On Chip 1.8V Voltage Regulator

- Program and Flight Mode Operation

- SPI Compatible

- Supply Voltage: 3.0V to 3.6V

- $\theta_{JC} = 1.81^{\circ} \text{C/W}$

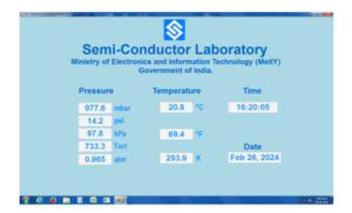

#### 2 CHANNELS SIMULTANEOUS SAMPLING 24 BIT Σ-Δ ADC Pressure Sensor Signal Conditioner (PSSC)

#### PRODUCT DESCRIPTION:

Pressure Sensor Signal Conditioner (PSSC) is developed for signal conditioning and digital conversion of the Pressure Sensor output data. It incorporates 2 Numbers of high resolution Sigma Delta ( $\Sigma\Delta$ ) ADCs, 2 Numbers of Eight Bits IDACs along with the calibration and over-range detection unit for each  $\Sigma\Delta$  ADC. User can communicate with any of the ADC through SPI interface using one bit channel address. There are two modes of operation: Program mode and Flight mode. User can select any of the modes through a primary input pin. Each  $\Sigma\Delta$  ADC uses a second order modulator with a Programmable Gain Amplifier (PGA) and on-chip offset and gain calibration. It converts the analog input signal into a digital pulse train whose average duty cycle represents the digitized signal information. The pulse train is then processed by a digital sinc3 filter to produce a digital output. The output data rate of  $\Sigma\Delta$  ADC is programmable. Each 8-bits current DAC is available with three different ranges: 0.5mA, 1mA and 2mA. The device interface is SPI Compatible.

- Two ΣΔ ADCs

- 24 Bits resolution

- PGA from 1 to 128 in binary steps

- Programmable Data Rate

- INL: 0.003%

- 19 Bits ENOB (PGA = 1, OSR=2047)

- On-chip Offset and Gain Calibrations

- Over Range Detection

- Data Format Selection

- Fully Differential Reference Inputs

- Two Offset DACs (ODACs)

- 8 Bits resolution

- Programmable up to half of full scale range at each PGA.

- Two Current DACs (IDACs)

- 8 Bits resolution

- Programmable Full Scale Ranges of 0.5mA, 1mA and 2mA.

- Precision on-chip 2.5V Reference

- Accuracy: ±1%, Drift: ±36ppm/°C

- On Chip Temperature Sensor

- Program and Flight Mode Operation

- SPI Compatible

- Supply Voltage 3.0V To 3.6V

# SINGLE CHANNEL 24 BIT CAPACITANCE TO DIGITAL CONVERTER (ASC)

#### **PRODUCT DESCRIPTION:**

Accelerometer Signal Conditioner (ASC) is a Sigma Delta Modulator based high resolution Capacitance-to-Digital Converter. It senses the change in the differential capacitance connected at the input and produces a 24 Bit digital code proportional to this change. This device is developed for sensing the capacitance change of MEMS based Accelerometer and can be used in other similar applications as well. The capacitance to be sensed can be directly connected at the input of this device.

ASC incorporates a Second Order Sigma Delta ( $\Sigma\Delta$ ) Modulator. The  $\Sigma\Delta$  Modulator converts the difference in the input differential capacitors into a digital 1 bit pulse train whose average duty cycle represents the digitized signal information. The pulse train is then processed by a digital sinc3 filter to produce a digital output.

#### **Features:**

- 24 Bits No Missing Codes

- Full Scale Input Capacitance Range CFS Up To ±4pf

- Nominal Capacitance Range CO Up To 17.75pf

- INL: 0.04%

- 18 Bits Effective Resolution

- Programmable Data Output Rates Up To 8kSPS

- On Chip Temperature Sensor

- On-chip Offset & Gain Calibration

- SPI Compatible

- 3.0v To 3.6v

- 180nm SCL Cmos Standard Logic Process

- Esd Protection Upto ±3kv HBM

## 10-BIT,1.5MSPS, SUCCESSIVE-APPROXIMATION -REGSITER (SAR) ANALOG TO DIGITAL CONVERTER

#### **PRODUCT DESCRIPTION:**

The 10-bit SAR is a monolithic CMOS analog-to-digital converter capable of converting analog input signals into 10-bit digital word up to 1.5 Mega samples per second (MSPS) in serial and parallel mode. This converter uses a SAR architecture, operating on a single 3.3V power supply, device achieves 10-bits effective resolution and consumes <5mW power. The inputs provide a full scale input swing equal 0.65V to 2.65V. Full scale input range is recommended for optimum performance. The ASIC is fabricated in 180nm SCL CMOS Standard Logic Process.

#### **FEATURES:**

Operating Voltage: 3.3V

Resolution: 10-BitData Rate: 1.5MSPS

Input Range: 4Vp-p Differential Ended

No missing code Guaranteed

Output Data Format: Straight Binary (Serial and Parallel)

Power Consumption < 5mW</li>

SCL's 180nm CMOS Technology

Operating Temperature (TA): -55°C to +125°C

Packaged in 64 Pins CQFP

# 12-BIT,1MSPS, 7-CHANNEL SUCCESSIVE-APPROXIMATION-REGSITER (SAR) ANALOG TO DIGITAL CONVERTER

#### **PRODUCT DESCRIPTION:**

The SC1260-0T2 device is a low-power; seven channel CMOS 12-bit Successive Approximation analog-to-digital converter specified for conversion throughput rates of 50kSPS to 1MSPS. The converter is based on successive approximation register architecture with an internal track-and-hold circuit. The device can be configured to accept up to seven input signals at inputs INO through IN6 and performs a 12-bit successive approximation analog-to-digital conversion in a nominal period of 16 clock cycles. The output serial data is straight binary and is compatible with serial interfaces. The 12-bit digital output has a tri-state control allowing the connection of multiple SC1260-0T2. This provides the ability to interface many sensor voltage readings to the digital processor data bus. The full-scale range is determined by analog supply voltages. The analog supply (VA) can range from 3.0 V to 3.3V, and the digital supply (VD) can range from 3.0 V to VA. Normal power consumption using a 3.3V supply is < 20mW for 16MHz SCLK and <7mW for 1MHz SCLK.

- Resolution: 12Bits

- Sampling Frequency: 50KSPS to 1MSPS

- No missing code Guaranteed

- Output Data Format : Straight Binary

- Operating Voltage: 3.3V

- Power Consumption < 20mW for 16MHz SCLK and <7mW for 1MHz SCLK</li>

- Input Range :3.3V Single Ended

- Package: 16 Lead Flat Package

- Øjc=7.1° C/W

- Technology: 180nm SCL CMOS Standard Logic Process-55ºCto+125ºC

- Packaged in 48 Pin CFP

# 12-BIT 200 MSPS CURRENT STEERING DAC (Digital to Analog Converter)

#### **PRODUCT DESCRIPTION:**

The SC9023-0 is integrated 12-bit 200MSPS digital-to-analog converter with a tunable full-scale output current from 2mA to 20mA and having two complementary outputs. It has an on-chip precise low drift voltage reference of 1.2V. SC9023-0 can also operate with an external reference. This may improve the DC accuracy if the external reference circuitry is superior in its drift and accuracy. Latches are provided for high-speed synchronization providing better AC characteristics for DAC. The ASIC is fabricated in 180nm SCL CMOS technology.

#### **FEATURES:**

Operating Voltage: 3.3V/1.8V

Resolution: 12BitsData Rate: 200MSPS

Full Scale Current: 2mA to 20mA

• On Chip Voltage References

Input straight Binary Format

Package: 64 PIN CQFP

Radiation hardened (TID) up to 300Krad(Si)

# INTERFACE, SUPERVISORY, AMPLIFIERS & DRIVERS

#### **RS422 TRANSCEIVER**

#### **PRODUCT DESCRIPTION:**

RS422 (SC1604-0) is a low power differential line transceiver designed for multi-point data transmission standard RS422 applications. The CMOS design offers significant power saving over its bipolar counterpart without sacrificing ruggedness against ESD damage. It offers a choice of active-high or active-low inputs. The device is designed for line/bus transmission at switching rates up to 5 MHz. The device can operate over a large temperature range -55°C to +125°C and it is packaged in ceramic-16 pin package.

- Operates from Single 3.3V V<sub>cc</sub>

- Integrated 3.3V to 1.8V linear voltage regulator

- Switching Rates up to 5 MHz

- Transmission Rate up to 10 Mbps

- Receiver input sensitivity of 400mV guaranteed over the entire power supply range

- Designed for RS422 applications

- Fail safe feature guarantees high output state when receiver inputs are left open

- Common Mode Output Voltage Range: 0V to 3V

- SCL's 180nm CMOS Technology

#### **QUAD RS422 DRIVER**

#### **PRODUCT DESCRIPTION:**

Quad RS-422 (SC1011-0) is a differential line driver that operates with a 3.3V power supply. The enable function is common to all four drivers and offers a choice of active-high or active-low inputs. Each driver has a separate input and output pins for full-duplex bus communication designs. The device is designed for balanced bus transmission at switching rates up to 5 MHz. The device can operate over a large temperature range -55°C to+125°C and it is packaged in ceramic-16 pin package.

- Operates from Single 3.3V V<sub>cc</sub>

- Switching Rates up to 5 MHz

- Transmission Rate up to 10 Mbps

- Differential-State Outputs

- Designed for Multipoint Bus Transmission

- Common Mode Output Voltage Range: 0V to 3V

- SCL's 180nm CMOS Technology

#### **RS485 TRANSCEIVER**

#### **PRODUCT DESCRIPTION:**

RS485 (SC1603-0) is a low power differential line transceiver designed for multi-point data transmission standard RS485 applications. The enable function is different for both transmitter and receiver lines. It offers a choice of active- high or active-low inputs. The device is designed for line/bus transmission at switching rates up to 5 MHz The device can operate over a large temperature range -55°C to +125°C and it is packaged in ceramic-16 pin package.

- Operates from Single 3.3V V<sub>cc</sub>

- Integrated 3.3V to 1.8V linear voltage regulator

- Switching Rates up to 5 MHz

- Transmission Rate up to 10 Mbps

- Receiver input sensitivity of 200mV guaranteed over the entire power supply range

- Designed for RS485 applications

- Fail safe feature guarantees high output state when receiver inputs are left open.

- Common Mode Output Voltage Range: 0V to 3V

- SCL's 180nm CMOS Technology

# Addressable Synchronous/Asynchronous Differential Receiver (ASDR)

#### **DESCRIPTION:**

ASDR (Addressable Synchronous / Asynchronous Differential Receiver) is a mixed signal ASIC being developed under Technology Development Project (TDP). It has three RS422 differential receivers, one RS422 differential transmitter, Digital Serial to Parallel Converter, on chip oscillator, Linear Voltage Regulator (LVR) and power on reset circuit.

The ASIC takes up to three RS422 differentials inputs and convert it into 16 bit CMOS parallel Signal with different modes.

Mode-0: synch 24 bit data, with a strobe width of 24 bit Mode-1: synch 24 bit data, with a strobe width of 1 bit

Mode-2: synch 16 bit data, with gated clock

Mode-3: asynchronous 8 bit UART

- Synchronous / Asynchronous serial (RS422) to parallel converter with different modes.

- 4 Operating Mode (3 Synchronous and 1 Asynchronous)

- 5Bit Local Address

- 10 Mbps Speed (as per RS422 Std.)

- Common Mode Voltage: 0.5 V to 2.7V

- RS 422 Input Sensitivity: 0.2V to 3.3V

- On Chip Oscillator: 3.12 MHz

- On Chip LVR:1.8V±4%, 50mA

- Operating Temperature: -55°C to +125°C

- Power Supply: AV<sub>DD</sub>-3.3V, DV<sub>DD</sub>-1.8V

- Current Consumption: ≤10mA

#### **High Speed Quad LVDS Driver**

#### **PRODUCT DESCRIPTION:**

The SC1002-1 is a quad, low-voltage, differential signalling (QLVDS) driver specifically designed in a low-power and fast point-to-point baseband data transmission standard.

The intended application of these devices and signalling technique is point-to-point data transmission over controlled impedance media of approximately 100 ohm. The transmission media may be printed-circuit board traces, backplanes or cables.

- Single Power Supply 3.3V ±0.3V

- LVTTL/CMOS logic input levels and LVDS output levels

- 400 Mbps (200 MHz) switching rates

- ±350 mV differential signalling

- Power dissipation 26 mW Typical per driver at 200 MHz (VDD=3.3V)

- Propagation delay ≤ 5 nsec.

- Compatible with ANSI/TIA/EIA-644 LVDS standard

- Operating Temperature (T<sub>A</sub>): -55<sup>o</sup>C to +125<sup>o</sup>C

- Driver output at high impedance when disabled or with VDD = 0

- Cold sparing at LVDS output pins.

- Pin compatible with QLVDS driver LVDS31

- ESD protection upto class-1 (< 1999V)</li>

- Latch up current protection up to ±100mA

- Hermetic sealed 16 pin Flat package

- Package  $\Theta_{1c} = 3.1$  °C/Watt

- SCL's 180nm CMOS Technology

#### **High Speed Quad LVDS Receiver**

#### **PRODUCT DESCRIPTION:**

The SC1003-1 is a quad, low-voltage, differential signalling (QLVDS) line receiver specifically designed in a low-power and fast point-to-point baseband data transmission standard.

Any of the four differential receivers provides a valid logical output state with a  $\pm 100$ mV differential input voltage within the input common-mode voltage range. The circuit features an internal fail safe function to ensure a known output state in case of an input short circuit or floating. The intended application of these devices and signalling technique is point-to-point data transmission over controlled impedance media of approximately 100 ohm. The transmission media may be printed-circuit board traces, backplanes or cables.

- Single Power Supply 3.3V ±0.3V

- LVDS input levels and CMOS logic output levels

- 400 Mbps (200 MHz) switching rates

- Differential input thresholds ± 100mV

- Open circuit fail safe function

- Power dissipation 76 mW Typical per receiver at 200MHz (VDD=3.3V)

- Propagation delay ≤ 5 nsec.

- Compatible with ANSI/TIA/EIA-644 LVDS standard

- Operating Temperature (TA): -55°C to +125°C

- Cold Sparing at LVDS input pins

- Pin compatible with QLVDS receiver LVDS33

- ESD protection upto class 1 (< 1999V)

- Latch up current protection ±100mA

- SCL's 180nm CMOS Technology

- 16-Pin Ceramic-Dual-Flat package

- Package  $\Theta_{1c} = 3.1$  °C/Watt

- FM Qualified as per MIL STD 883

#### 3.3V Voltage Supervisory Circuit

#### **PRODUCT DESCRIPTION:**

This device is a 3.3V supervisory circuit that reduces the complexity required to monitor supply voltage in microprocessor systems. This device will significantly improve accuracy and reliability relative to discrete solutions. This device has following key functions

- A reset output during power-up, power down and brownout conditions

- A precision threshold voltage detector for monitoring a power supply.

- An active-low, manual-reset input.

- Analog Supply Voltage is 3.3V

- Precision Supply Voltage Monitor:3.195 V Threshold

- Reset Pulse Width 178ms (typical)

- Precision threshold detector 0.61V threshold

- Operating Temperature (T₄): -55°C to +125°C

- Low Power Dissipation.

- Packaged in 8-Pin CFP package.

- SCL's 180nm CMOS Technology

# Quad Core Charge to Voltage Amplifier (QCCVA)

#### **PRODUCT DESCRIPTION:**

Charge Amplifier is a signal conditioner which conditions the signal from Vibration, Shock and Acoustic transducers. Quad Core Programmable C-to-V Amplifier (EF1008-0) contains 4 cores of programmable C-to-V amplifier. Each of the cores can be programmed independently through input control signals. The user can select any of the gain and DC output value by applying the appropriate value at the control inputs.

Programmable C-to-V amplifier is targeted for vibration, acoustic and other measurements having charge as input. The device converts input charge to voltage. Charge to Voltage converter is followed by the Programmable Gain Amplifier (PGA) which provides 6 programmable gains from 1 to 32 binary steps. The DC level of the output is shifted up to four different values. The user can set the values of PGA and DC output level using input control signals.

- Analog Supply Voltage is 5V.

- Digital Supply is 3.3V.

- PGA: 1 to 32 in Binary Steps.

- Output DC level Adjustment: 0, 1.25, 1.65 and 2.5

Volt.

- Operating Temperature (T<sub>△</sub>): -55°C to +125°C

- Low Power Dissipation.

- Packaged in 64 Pin CQFP package.

#### **Capacitance-to-digital Converter (CDC)**

#### **PRODUCT DESCRIPTION:**

SC1602 is a high resolution, Sigma Delta based Capacitance-to-digital Converter (CDC). The capacitance to be measured is connected directly to the device inputs. The device also offers offset and nonlinearity correction (upto second order) of the sensors with capacitances upto 28pf. It can also accept upto 28pf common mode capacitance. It is designed for single ended capacitive sensors (both terminals must be available). The serial interface is SPI compatible.

CDC is operated with supply of analog voltage 3.3 V and digital voltage 1.8 V across the temperature range of -40°C to +125°C.

- 12-bit resolution

- Wide Capacitance range of 4 pf to 28 pf.

- Input offset capacitance range of 4 pf to 28 pf.

- Programmable output data rate of upto 4 KHz.

- SPI compatible serial interface.

- Non-linearity correction of sensor (up to 2nd order)

#### **OPERATIONAL AMPLIFIER**

#### **PRODUCT DESCRIPTION:**

Operational amplifier (SC1403-0) is designed as an IP block. This chip consists of 2 nos. of internally compensated CMOS input op-amps in folded cascade architecture. First op-amp has internal bias resistor whereas second op-amp requires approx.  $33k\Omega$  external bias resistor.

- Open loop Gain > 80db

- Settling Time (0.05%) < 40ns

- Unity Gain Bandwidth > 32MHz

- Supply:±1.65V(Dualsupply) +3.3V (single supply)

- Power Dissipation < 15mW

- Slew Rate: 70 V /μs

- Input offset voltage ±6.7mV

- Offset voltage drift 4μV/°C

- Load Resistance > 1KΩ

- Test Circuit

- Load Capacitance < 30pF SCC 180nm CMOS Technology

#### **INSTRUMENTATION AMPLIFIER**

#### **PRODUCT DESCRIPTION:**

Programmable Current feedback instrumentation amplifier (SC1406-0) is an IP based solution for high CMRR applications of the order of 80db and above. The output voltage swing is completely independent of input common mode voltage. It has six independent closed loop gain options which can be selected through two control lines. It offers Single supply operation and consumes low power.

- 3.3V single power supply

- CMOS logic input levels for digital I/O

- Low power dissipation (< 2mW@3.3Vstatic)</li>

- Minimum CMRR: 87.6dB (DC)

- Minimum CMRR: 66dB at 10KHz

- Minimum PSRR: 63.20 dB

- Minimum PSRR: 54.58 dB at 1KHz

- High Input Impedance

- Bandwidth (G=1): 1.13MHz

- Six programmable gain option

- Operating Temperature: -55°C to +125°C

- SCL's 180nm CMOS Technology

- Hermetic sealed 14 pin DIP

#### SINGLE CHANNEL, 5MHz, 850pF, BIPOLAR CLOCK DRIVER

#### **PRODUCT DESCRIPTION:**

The EF1103-0 is a high-speed clock driver specifically designed and packaged in a hermetic sealed ceramic flat-16 lead (SOP) package for use in high speed CCD and time delay integration (TDI) detector clocks. The intended application of these devices is to drive high capacitive CCD loads of the order of ~850pF and fast rise / fall requirements.

- 3.3V power supply for VDD

- 5 MHz operating frequency

- Single channel input

- Input level shifters

5V ≥ VL ≥-5V

9V ≤ VH ≤ 14V

- Low power dissipation (0.7W at 5MHz with output load of 850pf)

- 20ns t<sub>R</sub>/t<sub>E</sub> at 850pF load

- 30 ns T<sub>PLH</sub>/T<sub>PHL</sub> delay

- Matched rise and fall time < 2ns

- Matched propagation delay match < 2ns</li>

- 16 pin Lead Flat package (SOP)

- Operating Temperature: -55°C to +125°C

#### FOUR CHANNEL, 5MHz, 850pF, BIPOLAR CLOCK DRIVER

#### **PRODUCT DESCRIPTION:**

The EF1104-0 is a high-speed clock driver specifically designed and packaged in a hermetic sealed ceramic flat-48 lead DIL package for use in high speed CCD and time delay integration (TDI) detector clocks.

The intended application of these devices is to drive high capacitive CCD loads of the order of  $\sim$ 850pF and fast rise / fall requirements.

- 3.3V power supply for VDD1

- 5 MHz operating frequency

- Four channel input

- Input level shifters

5V ≥ VL ≥- 5V

9V ≤ VH ≤ 14V

- Low power dissipation (5W at 5MHz with output load of 850pf on each output)

- 15ns t<sub>R</sub>/t<sub>F</sub> at 850pF load

- 25/27 ns T<sub>PLH</sub>/T<sub>PHL</sub> delay

- Matched rise and fall time <2ns

- Matched propagation delay match <3ns</li>

- Hermetic sealed 48 pin Lead Flat package (DIL)

- Operating Temperature: -55°C to +125°C

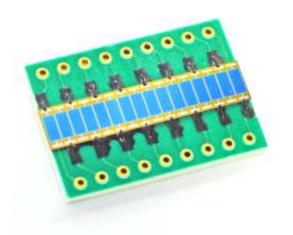

#### FOUR CHANNEL, 5MHz, 3000pF, CLOCK DRIVER

#### **PRODUCT DESCRIPTION:**

The FT CCD detectors are envisaged to use in high-resolution application designs. Detector clocks requirements for external TDI operation are more complex due to large capacitive drive requirements. The clock drivers need to drive a high capacitive load ~3000pF. A 4 channel clock driver having one 3000pF, one 150pF, one 50pF, and one 25pF channel driving capabilities has been developed.

#### **FEATURES:**

- 3.3V power supply for VDD1

- 5 MHz operating frequency

- Four channels input

- Input level shifters

0.6V ≥ VL ≥ 0V

12V ≤ VH ≤ 14V

- Low power dissipation (<4W at 5MHz)</li>

- t<sub>R</sub>=50ns, t<sub>F</sub>=44ns at 3000pF load

- tr=5ns, tf=6ns at 150pF load

- $T_{PLH} = 24$ ns,  $T_{PHL} = 25$ ns delay

- Matched rise and fall time < 7ns

- Matched propagation delay match < 2ns</li>

- Hermetic sealed 16 pin Quad flat package

- Operating Temperature: -55°C to +125°C

FM Qualified as per MIL STD 883

FT CCD Imager for OCM-III

This device is successfully used in OCM payload of

This device is successfully used in OCM payload of Oceansat-III mission.

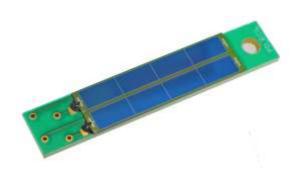

#### TWELVE CHANNEL, 1MHz, 3000pF, CLOCK DRIVER

#### **PRODUCT DESCRIPTION:**

The FT CCD detectors are envisaged to use for high-resolution application designs. Detector clocks requirements for external TDI operation are more complex due to large capacitive drive requirements. The clock drivers need to drive a high capacitive load ~3000pF. A 12 channel clock driver having four 3000pF channel and eight 150pF channel driving capabilities has been developed.

- 3.3V power supply for VDD1

- 1 MHz operating frequency

- Twelve channels input

- Input level shifters

0.6V ≥ VL ≥ 0V

12V ≤ VH ≤ 14V

- Low power dissipation (<5W at 1MHz)</li>

- $t_R = 60 \text{ ns}, t_E = 5 \text{ ns at } 3000 \text{pF load}$

- $t_R=6$ ns,  $t_F=7$  ns at 150pF load

- $T_{PH}$ =26ns,  $T_{PHI}$ =27ns delay

- Matched rise and fall time <7ns

- Matched propagation delay match <2ns</li>

- Hermetic sealed 64 pin Ceremic Quad Flat package

- Operating Temperature: -55°C to +125°C

#### FOUR CHANNEL, 5MHz, 1000pF, CLOCK DRIVER

#### **PRODUCT DESCRIPTION:**

The EF1105-0 is a high speed non-inverting, quad CMOS driver. It is capable of running at clock rates up to 5 MHz and features 0.6A typical peak drive capability and a nominal on-resistance of just  $3\Omega$ . The EF1105-0 is ideal for driving highly capacitive loads, such as storage and vertical clocks in CCD applications. It is also well suited to ATE pin driving, level-shifting, and clock-driving applications. Each output can be switched to either the high (VH) or low (VL) supply pins, depending on the related input pin. The inputs are compatible with both 3V and 5V CMOS and TTL logic. The output enable (OE) pin can be used to put the outputs into a high-impedance state. This is especially useful in CCD applications, where the driver should be disabled during power down. The driver has fast rise and fall times, which are typically matched to within 20ns (for CLoad=1nF). The ceramic flat pack (16 Lead) is taken for packaging.

- 5 MHz operating frequency

- Wide output voltage range

- Four channels input

- Input level shifters

8V ≥ VL ≥ -5V

0V ≤ VH ≤ 15V

- Low power dissipation (5W at 5MHz with output load of 1000 of on each output)

- $t_R = 22 \text{ns}, t_F = 20 \text{ns} @ 1000 \text{pf load}$

- t<sub>PLH</sub>= 38ns, t<sub>PHL</sub>=41ns delay @ 1000pf load

- Matched rise and fall time <3ns</li>

- Matched propagation delay match <4ns</li>

- Peak drive, 0.6A

- On-resistance, 3Ω

- TTL/CMOS input-compatible

- 16 pin Ceramic Dual Flat package

- Operating Temperature: -55°C to +125°C

# STANDARD DIGITAL DEVICES

#### **HEX BUFFER SCL4050**

#### **PRODUCT DESCRIPTION:**

SC1013-0 is non-inverting hex buffer. It consists of 6 buffer stages, providing high noise immunity and a stable output. The device can operate over a large temperature range from -55°C to +125°C. Device is packaged in a hermetic sealed 16-pin ceramic dual Flat pack.

- Power Supply Voltage 2.5V to 5.5V

- Cold Sparing feature at inputs

- Typical Propagation Delay: 5ns at VDD=5.0V, CL=30pF, TA=25°C

- Low Power Dissipation, IDD (typ.) < 1μA

- Balanced Propagation Delays and transition times

- Symmetrical Output loading I<sub>OH</sub> = I<sub>OL</sub> = 8mA

- Operating Temperature: -55°C to 125°C.

- Pin compatible with 54HC4050

- Package ΘJC = 3.1°C/Watt

- 16-Pin Ceramic-Dual-Flat package

- SCL's 180nm CMOS Technology

#### **OCTAL BUFFER SCL541**

#### **PRODUCT DESCRIPTION:**

SC9029-0 is radiation hardened non-inverting Octal buffer / Line driver have three state output. The output enable pins (OE1 and OE2) control the three-state outputs. If either enable signal is high the outputs will be in the high impedance state. For data output both enables (OE1 and OE2) must be low.

- Power Supply Voltage 5V ±0.5V

- Cold Sparing feature at Input pins

- Three state outputs

- Low Power Dissipation, IDD (Max.) < 1mA

- Balanced Propagation Delays. T<sub>PLH</sub> = T<sub>PHL</sub>

- Symmetrical Output Impedance

- $I_{OH} = I_{OL} = 8 \text{ mA}$

- Operating Temperature:-55°C to 125°C.

- Pin compatible with HC541

- 20 Pin Ceramic-Dual-Flat package

- SCL's 180nm CMOS Technology

#### **16 BIT BUFFER 3-STATE OUTPUT**

#### **PRODUCT DESCRIPTION:**

SC1004-2 16-bit buffer and line driver is designed for low-voltage (VDD =3.3V) operation, these devices can be used as four 4-bit buffers, two 8-bit buffers, or one 16-bit buffer. The outputs, which are designed to source or sink up to 7mA, include equivalent small series resistors to reduce overshoot and undershoot. zActive bus-hold circuitry holds unused or undriven inputs at a valid logic state. These devices are fully specified for hot-insertion applications using IOFF and power-up 3-state. The IOFF circuitry disables the outputs, preventing damaging current backflow through the devices when they are powered down. The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict.

- Single Power Supply 3.3V ±0.3V

- Cold sparing feature at I/O

- Output Ports Have Equivalent 22-W Series

Resistors, so No External Resistors are required.

- 5V tolerant inputs for interfacing 5V logic with 3.3V VDD

- IOFF and power-up 3-state support hot Insertion

- Bus Hold on data inputs eliminates the need for external pull-up / pull-down resistors

- Distributed VDD and GND pins minimize highspeed switching noise

- Flow-through architecture optimizes PCB layout

- Output loading 7 mA

- 6.5 ns typical propagation delay

- Low power dissipation (<2mW at 3.6V static)

- Operating Temperature: -55°C to 125°C.

- Device packaged in hermetic sealed 48 pin Ceramic Dual Flat package.

- Pin compatible with 16 Bit Buffer LVTH162244.

- Package  $\Theta_{10} = 2.7^{\circ}$ C/Watt

- SCL's 180nm CMOS Technology

#### **16 BIT TRANSCEIVER 3-STATE OUTPUT**

#### **PRODUCT DESCRIPTION:**

SC1124-0 16-bit Transceiver is designed for low-voltage (VDD=3.3V) operation, but with the capability to provide a TTL interface to a 5V system environment. These devices can be used as two 8-bit Transceivers or one 16-bit Transceiver.

The outputs, which are designed to source or sink up to 10 mA, include equivalent 22-W series resistors to reduce overshoot and undershoot. Active bus-hold circuitry holds unused or undriven inputs at a valid logic state. Use of pullup or pull down resistors with the bus-hold circuitry is not recommended. These devices are fully specified for hot-insertion applications using loff and power-up 3-state. The IOFF circuitry disables the outputs, preventing damaging current backflow through the devices when they are powered down. The power-up 3-state circuitry places the outputs in the high-impedance state during power up and power down, which prevents driver conflict.

- 3.3V power supply for core and I/O pads

- Cold sparing feature at I/O

- Output Ports Have Equivalent 22-W Series Resistors, so No External Resistors are required.

- 5V tolerant inputs for interfacing 5V logic with 3.3V VDD

- IOFF and power-up 3-state support hot Insertion

- Bus Hold on data inputs eliminates the need for external pull-up / pull-down resistors

- Output loading more than 7 mA

- 6.2 ns typical propagation delay

- Typical V<sub>OLP</sub> (Output Ground Bounce) < 0.8 V at VDD = 3.3 V, T<sub>A</sub> = 25°C

- Low power dissipation <2mW at 3.6V static</li>

- Operating Temperature: -55°C to 125°C.

- Pin compatible with 16 Bit Buffer LVTH162245.

- Package Θ<sub>IC</sub> = 2.7ºC/Watt

- SCL's 180nm CMOS Technology

- Qualified as per MIL STD 883

#### 3.3V QUAD 2-INPUT NAND GATE SCL4093

#### **PRODUCT DESCRIPTION:**

SC1118-0 is a Quad Two input NAND gate with Schmitt trigger action on both inputs. Schmitt trigger is a comparator which triggers at different points for positive and negative going signals and the difference between positive voltage (VT+) and negative voltage (VT-) is the Hysteresis voltage (VH). All outputs have equal source and sink currents.

- Operating Voltage 3.3V ± 0.3V

- Schmitt-trigger on each input with no external components.

- Noise immunity greater than 50%

- Equal source and sink currents

- No limit on input rise and fall time

- Hysteresis voltage (any input),  $V_H = 0.8 \text{ V} (V_{DD} = 3.3 \text{ V})$ and  $T_A = 25 ^{\circ}\text{C}$

- TA = 25°C (Typical)

- VDD = 3.3V, VH = 0.8V

- Operating Ambient Temperature: -55°C to 125°C

- 14 pin ceramic Dual in line package / Ceremic Flat package

- Pin compatible with CD4093

- Package  $\Theta_{IC} = 7.17 \,^{\circ}\text{C/Watt}$

- SCL's 180nm CMOS Technology

- Qualified as per MIL STD 883

#### **5V QUAD 2-INPUT NAND GATE SCL4093**

#### **PRODUCT DESCRIPTION:**

SC1125 is a Quad Two input NAND gate with Schmitt trigger action on both inputs. Schmitt trigger is a comparator which triggers at different points for positive and negative going signals and the difference between positive voltage (VT+) and negative voltage (VT-) is the Hysteresis voltage (VH). All outputs have equal source and sink currents.

- Operating Voltage 5V ± 0.5V

- Schmitt-trigger on each input with no external components.

- Noise immunity greater than 50%

- Equal source and sink currents

- No limit on input rise and fall time

- Hysteresis voltage (any input)  $V_H = 1.6 \text{ V} (V_{DD} = 5.05 \text{ and } T_A = 25 ^{\circ}\text{C}$

- Operating Ambient Temperature: -55°C to 125°C

- 14pin ceramic flat package (CSOP)

- Pin compatible with CD4093

- Package  $\Theta_{IC} = 7.17 \, ^{\circ}\text{C/Watt}$

- SCL's 180nm CMOS Technology

## 3.3V HEX SCHMITT TRIGGER INVERTER SCL5414

#### **PRODUCT DESCRIPTION:**

SC1111-0 is a hex inverter with Schmitt trigger action on inputs. Schmitt trigger is a comparator which triggers at different points for positive and negative going signals and the difference between positive voltage (VT+) and negative voltage (VT-) is the Hysteresis voltage (VH).All outputs have equal source and equal sink currents.

- Operating Voltage 3.3V±0.3V

- Schmitt-trigger on each input with no external components.

- Noise immunity greater than 50%

- No limit on input rise and fall time

- Hysteresis voltage (any input)  $V_H = 1.04 V$  ( $V_{DD} = 3.3 V$  and  $T_A = 25 °C$

- Operating Ambient Temperature -55°C to 125°C

- 14-pin ceramic flat package (SOP) Pin compatible with 5414

- SCL's 180nm CMOS Technology

- Qualified as per MIL STD 883

## 5V HEX SCHMITT TRIGGER INVERTER SCL5414

#### **PRODUCT DESCRIPTION:**

SC1126-0 is a Hex Inverter with Schmitt trigger action on all inputs. Schmitt trigger is a comparator which triggers at different points for positive and negative going signals and the difference between positive voltage (VTP) and negative voltage (VTN) is the Hysteresis voltage (VH).

- Operating Voltage 5.0V± 0.5V

- Schmitt-trigger on each input with no external components.

- Cold sparing feature available at input pins

- Noise immunity greater than 50%

- No limit on input rise and fall time

- Hysteresis voltage (any input)  $V_H = 1.1V (V_{DD} = 5.0 \text{ V} \text{ and } T_A = 25^{\circ}\text{C}$

- Operating Ambient Temperature: -55°C to 125°C

- 14-pin ceramic flat package (SOP) Pin compatible with 5414

- SCL's 180nm CMOS Technology

- Qualified as per MIL STD 883

#### 8-CH ANALOG MUX DEMUX SCL4051

#### **PRODUCT DESCRIPTION:**